Blekinge Institute of Technology Doctorial Dissertation Series No. 02/01 ISSN 1650-2159 ISBN 91-7295-004-8

## **Software Design Conflicts**

## Maintainability versus Performance and Availability

Daniel Häggander

Department of Software Engineering and Computer Science Blekinge Institute of Technology Sweden

ISSN 1650-2159 ISBN 91-7295-004-8

© Daniel Häggander, 2001

Printed in Sweden Kaserntryckeriet AB Karlskrona, 2001

This thesis has been submitted to the Faculty of Technology, Blekinge Institute of Technology, in partial fulfilment of the requirements for the Degree of Doctor of Philosophy in Engineering.

#### **Contact Information:**

Daniel Häggander Department of Software Engineering and Computer Science Blekinge Institute of Technology Soft Center S-372 25 RONNEBY SWEDEN

Tel.: + 46 457 385819 Fax.:+ 46 457 271 25

email: Daniel.Haggander@bth.se URL: http://www.ipd.hk-r.se/dha

## **Abstract**

A major goal in software engineering is to reduce the cost of maintaining software systems. Finding design methods which make software more easily maintainable has thus been one of the most prioritized challenges during the past decade. While mainstream software design has concentrated on maintainability, other software disciplines e.g. high-performance computing and high-availability systems, have developed other design methods which primarily support the quality attributes that are more important in their areas. More recently, demands have been made for high performance and high availability in typical mainstream software. At the same time, traditional high-performance and high-availability systems tend to incorporate more advanced business functionality, i.e. different software disciplines have started to converge. The situation is not unproblematic since the software design methods developed for achieving performance and availability may have been developed with a limited influence from maintainability, and vice versa. It is thus important to identify and analyze emerging design conflicts.

In this thesis I have studied conflicts between maintainability design methods on the one hand, and performance and availability methods and techniques on the other. I present the results of four case-studies involving four different applications. It is a characteristic of these applications that half of the system can be regarded as a telecommunications system and the other as a typical main-stream system, i.e. all systems make high demands on performance and availability but also very high demands on high maintainability. In studying these applications, I have identified two major conflicts: granularity in dynamic memory usage and source code size. My results show that these two conflicts can cause problems of such amplitude that some applications become unusable. I found that conflicts in certain situations are inherent; in other cases they can be avoided - or at least reduced - by adjusting the design methods used. I have also shown that conflicts may quite simply be a matter of misconceptions. Ten guidelines have been combined into a simple process with the aim of helping software designers to avoid and reduce conflicts. A method which automatically reduces the dynamic memory conflict in object-oriented applications written in C++ has been developed, implemented and evaluated. Finally, I have defined optimal recovery schemes for high availability clusters.

## List of Papers

The present thesis is based on the following papers. References to the latter will be made using the roman numbers applied to the particular paper.

- [I] Daniel Häggander and Lars Lundberg, "Optimizing Dynamic Memory Management in a Multithreaded Application Executing on a Multiprocessor", in Proceedings of the 27th International Conference on Parallel Processing, Minneapolis, USA, pp. 262-269, August 1998.

- [II] Daniel Häggander and Lars Lundberg, "Memory Allocation Prevented Telecommunication Application to be Parallelized for Better Database Utilization", in Proceedings of the 6th International Australasian Conference on Parallel and Real-Time Systems, Melbourne, Australia, pp. 258-271, November 1999 (Springer Verlag).

- [III] Daniel Häggander, PerOlof Bengtsson, Jan Bosch and Lars Lundberg, "Maintainability Myth Causes Performance Problems in Parallel Applications", in Proceedings of the 3rd International IASTED Conference on Software Engineering and Applications, Scottsdale, USA, pp. 288-294, October 1999.

- [IV] Daniel Häggander and Lars Lundberg, "A Simple Process for Migrating Server Applications to SMPs", *Journal of System and Software 57*, pp. 31-43, 2001.

- [V] Daniel Häggander, Lars Lundberg and Jonas Matton, "Quality Attribute Conflicts Experiences from a Large Telecommunication Application", in Proceedings of the 7th IEEE International Conference on Engineering of Complex Computer Systems, Skövde, Sweden, pp. 96-105, June 2001.

- [VI] Daniel Häggander and Lars Lundberg, "Attacking the Dynamic Memory Problem for SMPs", in Proceedings of the 13th International ISCA Conference on Parallel and Distributed Computing Systems, Las Vegas, USA, pp. 340-347, August 2000.

- [VII] Daniel Häggander, Per Lidén and Lars Lundberg, "A Method for Automatic Optimization of Dynamic Memory Management in C++", in Proceedings of the 30th International Conference on Parallel Processing, Valencia, Spain, September 2001.

- [VIII]Lars Lundberg and Daniel Häggander, "Recovery Schemes for High Availability and High Performance Cluster Computing", *Research Report 2001:06*, ISBN:1103-1581, submitted for journal publication.

Related papers and work not included in this thesis are listed below, in chronological order.

[IX] Lars Lundberg and Daniel Häggander, "Multiprocessor Performance Evaluation of Billing Gateway Systems for Telecommunication Applications", in Proceedings of the 9th International ISCA Conference on Computer Applications in Industry and Engineering, Orlando, USA, pp. 13-18, December 1996.

- [X] Lars Lundberg and Daniel Häggander, "Bounding on the Gain of Optimizing Data Layout in Vector Processors", in Proceedings of ICS 98, the ACM International Conference on Supercomputing, Melbourne, Australia, pp. 235-242, July 1998.

- [XI] Daniel Häggander and Lars Lundberg, "Multiprocessor Performance Evaluation of a Telecommunication Fraud Detection Application", in Proceedings of the ARTES Graduate Student Conference, Västerås, Sweden, pp. 33-39, May 1999.

- [XII] Daniel Häggander and Lars Lundberg, "Ten Performance Guidelines for Balancing Software Quality Attributes when Developing Large Real-time Applications for Multiprocessors", *Technical Report 99:16*, ISSN:1103-1581, September 1999.

- [XIII] Lars Lundberg, Jan Bosch, Daniel Häggander and PerOlof Bengtsson, "Quality Attributes in Software Architecture Design", in Proceedings of the 3rd International IASTED Conference on Software Engineering and Application, Scottsdale, USA, pp. 353-362, October 1999.

- [XIV] Daniel Häggander, PerOlof Bengtsson, Jan Bosch and Lars Lundberg, "Maintainability Myth Causes Performance Problems in SMP Applications", in Proceedings of the 6th IEEE Asian-Pacific Conference on Software Engineering, Takamatsu, Japan, pp. 516-519, December 1999.

- [XV] Daniel Häggander, "Software Design when Migrating to Multiprocessors", Department of Information Technology, Uppsala University, in partial fulfilment of the requirements for the Degree of Licentiate of Engineering, ISSN:0283-0574, DoCS 112, Uppsala, November 1999.

- [XVI] Lars Lundberg, Daniel Häggander and Wolfgang Diestelkamp, "Conflicts and Trade-offs between Software Performance and Maintainability", a chapter in the book "Performance Engineering. State of the Art and Current Trends", pp. 56-67, 2001 (Springer Verlag).

- [XVII] Magnus Broberg, Daniel Häggander, Per Lidén and Lars Lundberg, "Improving the Performance of Multiprocessor Memory Management in Java", to appear in Java Report.

- [XVIII]Daniel Häggander, Per Lidén and Lars Lundberg, "A Method and System for Dynamic Memory Management in an Object Oriented-Program", *Patent Application No. 0002679-9*, Sweden, July 2000.

## Acknowledgments

This work has been carried out as part of the ARTES project "Design Guidelines and Visualization Support for Developing Parallel" at Blekinge Institute of Technology, Sweden. ARTES is a national research programme supported by the Swedish Foundation for Strategic Research (SSF).

First of all I would like to thank my supervisor *Professor Lars Lundberg*, whose skills in computer systems and unlimited patience have been a great benefit. Secondly, I wish to thank my previous supervisor, *Professor Hans Hansson*, whose tremendous ability to solve practical problems has been invaluable.

I wish to express my thanks to Ericsson Software Technology and the members of the FCC, BGw, DMO, SDP and READ projects, particularly *Jonas Matton*, for giving me the opportunity to study their work. Further, I thank SUN Microsystems and *Pär Känsälä* for all their help with multiprocessor hardware.

I would like to thank the my colleagues at the Department of Software Engineering and Computer Science at Blekinge Institute of Technology, and in particular *PerOlof Bengtsson*, *Magnus Broberg* and *Per Lidén*. A big thanks also goes to *Jane Mattison* for helping me with proof reading.

## **Contents**

| Software Design Conflicts        |

|----------------------------------|

| 1. Introduction 1                |

| 2. Quality Attribute Definitions |

| 3. Research Methods              |

| 4. Research Results              |

| 5. Related Work                  |

| 6. References                    |

| Paper Section                    |

| Paper I                          |

| Paper II                         |

| Paper III                        |

| Paper IV                         |

| Paper V                          |

| Paper VI                         |

| Paper VII                        |

| Paper VIII 117                   |

## **Software Design Conflicts**

# Maintainability versus Performance and Availability

#### 1. Introduction

A prioritized goal in software engineering is to reduce the cost of maintaining software systems. A strong focus on software maintenance is considered important since maintenance is responsible for the major part of the costs in a product's life-cycle [Pigoski 97].

Finding design methods which make software more easily maintainable has thus been one of the greatest challenges during the past decade, at least for mainstream software design. A strong focus on maintenance-related quality attributes such as maintainability, variability and modifiability, to mention just a few, has resulted in a number of new design methodologies, the best known of which include object-orientation, frameworks, multi-layer design and design patterns. A software designer today is expected to have knowledge of these methodologies and to know how to use them.

While mainstream software design has concentrated on maintainability, other software disciplines have continued to develop new design methods that are effective in their own particular area. High-performance computing, often concentrating on scientific application, has, with the aid of parallel processing technology, constantly improved performance limits. In hardware, the results are Symmetric MultiProcessors (SMP) and the dawn of onChip Multiprocessors (CMP). Multiprocessor technology is dependent on parallel execution, i.e. methods for developing parallel software have

been developed in order to benefit from the high capacity of multiprocessors; a widely used example is multithreading.

Another system design area is high-availability systems. The market for this kind of software has been limited primarily to critical systems, e.g. airplanes and telecommunication equipment. Historically, these systems have normally provided a limited degree of business functionality and have often been built on propriety hardware and software. It is in this context that software design methods supporting high-availability have been developed.

More recently, demands have been made for high performance and high availability also for mainstream software applications. At the same time, traditional high-performance and high-availability software applications tend to incorporate more advanced business functionality, i.e. different software disciplines have started to converge. As a result, it has become necessary to consider maintainability with respect to other quality attributes, e.g. performance and availability, when designing application software.

The situation is not unproblematic since the methods developed for achieving performance and availability may have been developed with a limited influence from maintainability, and vice versa. Methods developed in different disciplines may at worst be incompatible, i.e. the convergence uncovers software design conflicts. These may come as a surprise to developers.

It is thus important to identify and quantify emerging design conflicts. Further, conflicts must be investigated in detail in order to find possible strategies for avoiding or reducing them. In some cases, it may just be a matter of small method adaptations. In other cases, however, alternative design methods may prove necessary.

Identifying and defining conflicts on a quality-attribute level creates a number of difficulties. One major problem is that the definition, scope and meaning of quality attributes, especially maintainability, are not unanimously and objectively understood. Another problem is that conflicts between quality attributes are often indirect, i.e. created by the design methods used to improve the quality attributes rather than the quality attributes themselves.

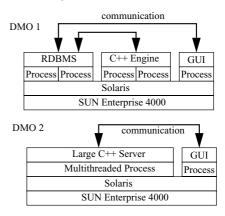

In this thesis, I have studied conflicts between maintainability design methods on the one hand, and performance and availability methods and techniques on the other. I present the results of four case-studies involving four different applications: Billing Gateway (BGw), Fraud Control Center (FCC), Data MOnitor Server (DMO) and Service Data Point (SDP), respectively. Three of the applications (BGw, FCC and SDP) have been developed by Ericsson Software Technology AB. They have, however, all been developed by different departments and different designers. The fourth application (DMO) was developed by students at Blekinge Institute of Technology, and was based on requirements defined by Ericsson Software Technology AB. All applications are what we refer to as "telecommunication support systems". It is a characteristic of this kind of systems that one part of the system can be regarded as a telecommunications system and the other as main-stream system, i.e. a system which telecommunication characteristics but also advanced business functions. The "in-between" position makes these systems interesting objects of study in software design conflicts.

In studying these applications, I have identified two major conflicts: granularity of dynamic memory usage, and source code size. My results show that these two conflicts can cause problems of such amplitude that some applications become unusable. I found that conflicts in certain situations are inherent; in other cases they can be avoided - or at least reduced - by adjusting the design methods used. I have also shown that conflicts may quite simply be a matter of misconceptions.

Ten guidelines have been combined into a simple process with the aim of helping software designers to avoid and reduce conflicts. A method which automatically reduces dynamic memory conflict in C++ has also been developed and tested on synthetic programs as well as in one of the case-study applications. Finally, I have suggested a method which simplifies the definition of favorable recovery schemes for high-availability and high-performance cluster systems.

The remaining pages are organized as follows. Section 2 presents definitions of the three quality attributes considered in this thesis. An overview of the research methods is given in Section 3. The results, in the form of an overview as well as individual summaries of eight papers, are presented in Section 4. In Section 5, prior and related work is provided and references are listed in Section 6. A paper section, including the eight papers on which this thesis is based, ends the thesis.

## 2. Quality Attribute Definitions

This section elaborates on definitions of three quality attributes: performance, availability and maintainability. Official definitions from [IEEE 90], [ISO 00] and [McCall 94] (The Encyclopedia of Software Engineering, 1994) are presented. The definitions, scope and meaning of quality attributes are, however, not unanimously or objectively understood, especially not maintainability [Kajko-Mattson 01]. This is, unfortunately, also a problem in the present thesis. In cases where I have used a definition of a quality attribute which differs from the official one, I have presented a definition of my own. In providing such definitions I do not mean to suggest that they are necessarily better or more correct than ready-existing ones; my hope is quite simply that they will make my thesis more readily understandable.

#### 2.1 Quality Attribute

"A quality attribute is a feature or characteristic that affect an item's quality. Syn: Quality factor", [IEEE 90]

This thesis focuses on the quality of an application, i.e. a combination of software and hardware. The definition used in the present thesis is thus:

"A quality attribute is a non-functional feature or characteristic that affect an application's quality" - definition used in this thesis

#### 2.2 Performance

**Performance** - "The degree to which a system or component accomplishes its designated functions within given constraints, such as speed, accuracy, or memory usage", [IEEE 90]

In many reports which discuss software quality attributes, attribute performance is excluded. However, a related attribute which is often used is efficiency.

**Efficiency (time-behavior)** - "The capability of the software product to provide appropriate response and processing times and throughput rates when performing its function, under stated conditions", [ISO 00]

The Encyclopedia of Software Engineering (1994) has a slightly different definition of efficiency, in which the latter is seen as a function of hardware.

**Software efficiency** - "The amount of computing resources required by a program to perform a function", [McCall 94]

The performance definition used in this thesis is a combination of the first two definitions, [IEEE 90] and [ISO 00], respectively.

**Performance** - "The degree to which an application accomplishes its designated functions within given constraints of appropriate response and processing times and throughput rates, under stated conditions" - definition used in this thesis

#### 2.3 Availability

**Availability** - "The degree to which a system or components is operational and accessible when required for use. Often expressed as a probability", [IEEE 90]

In ISO/IEC FDIS 9126-1:2000(E) availability is not included as a separate characteristic (attribute). Instead, ISO defines availability as a combination of maturity, fault tolerance and recoverability.

**Maturity** - "The capacity of the software product to avoid failure as a result of faults in the software", [ISO 00]

**Fault tolerance** - "The capability of the software product to maintain a specific level of performance in case of a software fault or of infringement of its specified interface", [ISO 00]

**Recoverability** - "The capability of the software product to reestablish a specified level of performance and recover the data directly affected in the case of a failure", [ISO 00]

There are no conflicts between the various definitions. The official definitions also comply with those used in this thesis. I have not made any attempt to measure the availability of the applications studied. When the level of availability is discussed, the discussion is based on previous experience and theoretical calculations based on figures given by equipment vendors.

#### 2.4 Maintainability

**Maintainability** - "The ease with which a software system or component can be modified to correct faults, improve performance, or other attributes, or adapt to a changed environment", [IEEE 90]

**Maintainability** - "The capability of the software product to be modified. Modifications may include corrections, improvements or adaptations of the software to changes in environment, and in requirements and functional specifications", [ISO 00]

The Encyclopedia of Software Engineering (1994) has a narrower definition of maintainability. Changes in environment or in requirements are not included in its definition of maintainability.

**Maintainability** - "Effort required to locate and fix an error in an operational program", [McCall 94]

The first two definitions eliminate the possibility of maintainability conflicting with some other attribute, thereby rendering a discussion about conflicts related to maintainability pointless.

A limitation of the scope to corrections, improvements or adaptations of the software to changes in the functional specifications makes the discussion of emerging conflicts more comprehensible.

With such a definition, maintainability can cause software design conflicts when it is required along with another attribute e.g., a design method used to improve maintainability can be in conflict with design methods normally used to fulfil other quality attributes such as performance and/or availability.

**Maintainability** - "The capability of the software product to be modified. Modifications may include corrections, improvements or adaptations of the software to changes in the functional specifications" - definition used in this thesis

In the studies considered here I have occasionally used source code size (lines of code) to measure maintainability. Measuring maintainability by means of the source code size is not a generally accepted method (there is indeed no generally accepted method). However, previous research indicates that maintenance costs are strongly related to the amount of source code [Granja & Barrancp-Garcia 97] [Li & Henry 93].

#### 3. Research Method

The overall research goal of this thesis is to:

Identify, quantify, analyze, and propose solutions for handling software design conflicts emerging when building maintainable applications with explicit and high demands on performance and availability.

In order to achieve my goal I have performed empirical studies on industrial cases, conducted interviews with designers and carried out experiments on synthetics programs as well as developed several prototypes in collaboration with industrial partners.

My thesis is divided into two parts: in the first I identify, quantify and analyze software design conflicts; and in the second I evaluate and propose solutions which avoid or reduce software design conflicts. The rest of this section gives an overview of the research methods used. More detailed information about the research methods used is given in the individual papers.

#### 3.1 Identify, Quantify and Analyze Conflicts

In order to identify, quantify and analyze design conflicts I have studied four different major telecommunication support applications written in C++ for use with UNIX. Three of the applications have been developed by Ericsson Software Technology AB. These are referred to as BGw, FCC, DMO and SDP. The last but one, DMO, was developed by students at Blekinge Institute of Technology. In three applications (BGw, FCC and DMO) maintainability is strongly prioritized. These applications are also very demanding with respect to performance due to real-time requirements on throughput and response time.

Symmetric multiprocessors and multithreaded programming have been used in order to give these applications a high, scalable performance. In the first three applications I studied conflicts between design methods for obtaining maintainability and methods for achieving performance. In the fourth study, the SDP case-study, I also had the opportunity to study availability aspects since this application

makes high demands on availability. The papers which identify, quantify and analyze software design conflicts are I, II, III, IV and V.

#### 3.2 Avoiding and Reducing Conflicts

Alternatives for avoiding or reducing software design conflicts can be divided into three groups: adjustment, exchange and compensation. In many situations it is quite simple to adjust a design method in such a way that the conflict is eliminated or reduced to an acceptable level. However, in some situations, the conflict is inherent, necessitating an exchange of at least one of the design methods. If the conflict is found at an early stage, it is often possible to find an alternative design method which is more tolerant. However, if the conflict is discovered in a late development phase or after delivery, compensating methods may prove very useful. By compensating methods I mean methods which reduce the effect rather than the actual cause of the conflict. Such methods have also shown to be cost effective when conflicts are identified at earlier stages. The papers which suggest solutions as to how to avoid and reduce conflicts are IV, V, VI, VII and VIII.

#### 4. Research Results

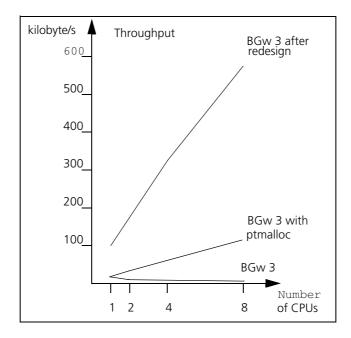

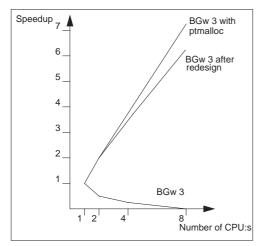

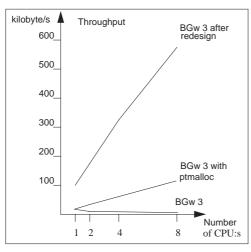

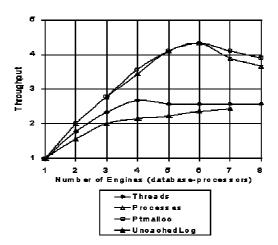

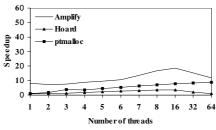

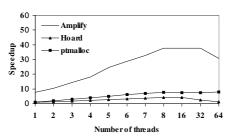

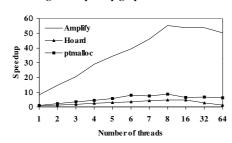

The first case-study was made on the BGw application. This is a mediation server written in multithreaded C++ and executed in UNIX on a symmetric multiprocessor. We found that the application has poor scale-up due to a bottleneck within the dynamic memory management. Two approaches to remove the bottleneck were evaluated: replacing the standard heap with a parallel heap (ptmalloc [Gloger]); and optimization of the application design by removing a number of heap allocations/deallocations respectively. Both methods were found to be efficient. However, the latter approach also improves performance when running the application on a single-processor computer.

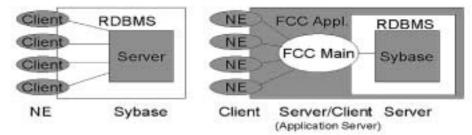

The same bottleneck was identified also in the next case-study (FCC), even though FCC is based on a third party relational database management system (RDBMS). The study showed that the bottleneck could be removed either by dividing FCC into a number of individual processes or by using ptmalloc. Using interviews with the developers of the FCC as a base, we established that the aim of developing a maintainable application was the major reason for the increased number of dynamic memory allocations, i.e. which caused the bottleneck. Our evaluation shows that an alternative design, based on rigid but exchangeable components, has much better performance characteristics.

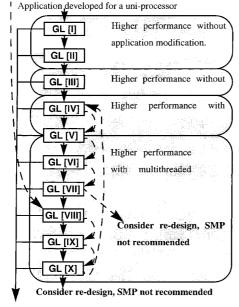

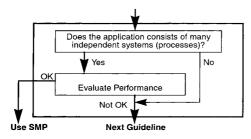

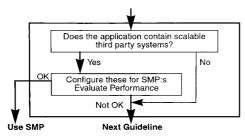

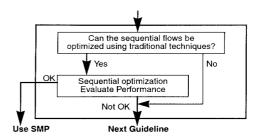

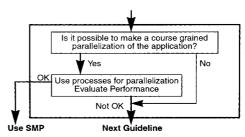

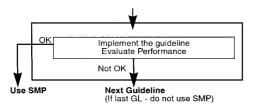

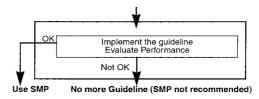

Using the results from the BGw and FCC studies as well as a study of a third application (DMO), I defined a simple design process based on ten guidelines. The process was designed with the aim of helping designers of applications to become more efficient in creating a balance between SMP performance and maintainability.

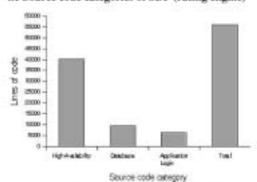

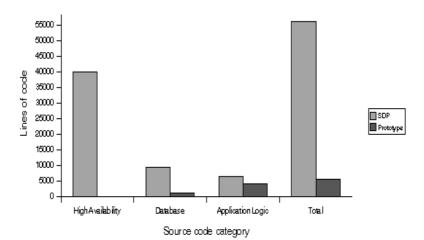

In the next case-study I checked if the quality attribute "conflict" which was identified in previous case-studies is bidirectional, i.e. if applications developed with a strong focus on run-time qualities such as performance and availability uncover unknown software design conflicts, resulting in maintainability problems. This was made possible by studying yet another telecommunication application (SDP). The application is part of a system which rates pre-paid subscribers in real-time. The result is on source code categorization, which showed that 85% of the source code was written in response to performance or availability demands. Work carried out by other researchers indicates that maintenance costs are strongly related to the amount of application code, i.e. the large amount of source code is a strong indication that

performance and availability have had a negative impact on maintainability.

Earlier studies carried out by the author indicate that methods used for obtaining maintainability often result in fine-grained dynamic memory usage, whereas a fine-grained dynamic memory usage can substantially damage performance, especially in multithreaded C++ applications running on SMPs.

To sum up, two major conflicts have been identified: granularity in dynamic memory usage, and source code size. My results show that these two conflicts can cause problems of such amplitude that some applications become unusable. I found that conflicts in certain situations are inherent; in other cases they can be avoided - or at least reduced - by adjusting the design methods. I have also shown that conflicts may quite simply be a matter of misconceptions.

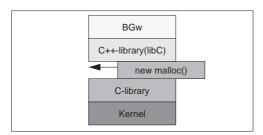

The simplest way, we have discovered, to attack the dynamic memory problem is to optimize the C library memory allocation routines. This is because such an optimization has low impact on the implementation of the application. However, reducing the usage of short-lived memory allocations gives the best result in terms of performance.

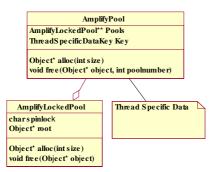

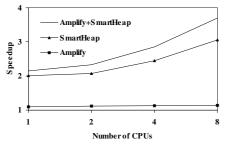

I have thus developed a pre-processor-based method named Amplify which can reduce the use of small and short-lived memory allocations in (object-oriented) C++ applications. Amplify does this by speculating on the temporal locality of dynamic memory allocations. Amplify makes it possible to achieve two goals at the same time. First, using Amplify is not more complicated than replacing the C library memory allocation routines. Second, the optimization is almost as effective as a reduction of the usage of short-lived memory allocation would be.

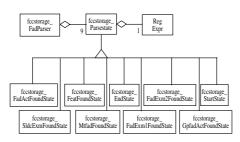

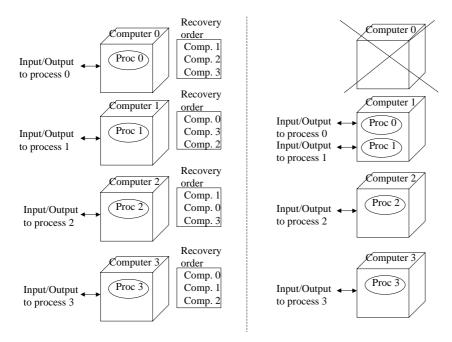

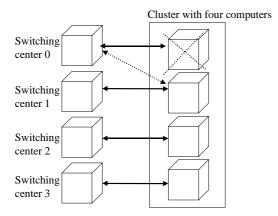

One software design conflict identified was source code size. Handling high-availability issues within the source code is one of the reasons for excessive code size. An example is fail-over cluster schemes defined in the application code. I have defined a very simple method for obtaining general recovery schemes which are optimal for a number of important cases, making it possible to move this feature from the application source code to cluster software.

The rest of the section presents individual summaries of the eight papers on which this thesis is based. I also acknowledge where results have been achieved with the aid of anyone other than my supervisor, professor Lars Lundberg.

## Paper I: Dynamic Memory Management in a Multithreaded Application Executing on a Multiprocessor

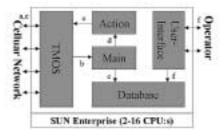

This paper reports the results from performance evaluations made on a large real-time application (Billing Gateway) executing on symmetric multiprocessors. The Billing Gateway (BGw) collects billing information about calls from mobile phones. The application has been developed by Ericsson. BGw is written in C++ (approximately 100,000 lines of code) using object-oriented design, and the parallel execution has been implemented using Solaris threads [Lewis 96].

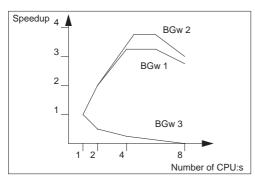

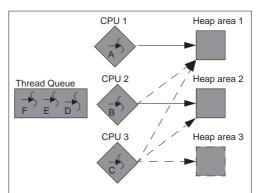

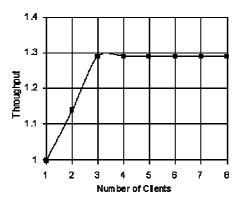

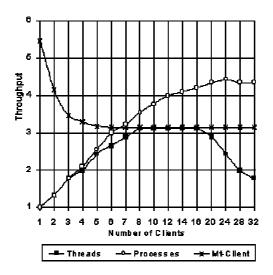

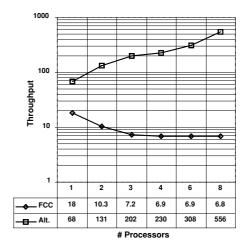

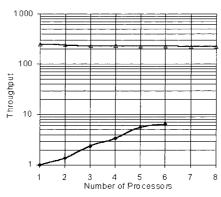

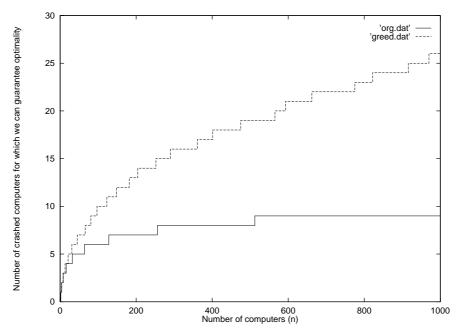

The parallel software design led us to believe that the application would scale-up well on a Symmetric MultiProcessor (SMP) [Hwang & Xu 98]. Performance evaluations showed, however, that the benefit of executing on multiprocessors was relatively small [IX]. One of the BGw versions failed to scale up at all (see Figure 1).

The major reason for this lack of benefit was that the standard sequential dynamic memory management combined with a large number of dynamic memory allocations and deallocations. The large number of allocations and deallocations is a result of the way in which the object-oriented design was used. This paper compares two approaches for improving the performance of the BGw: replacing the standard heap with a parallel heap (ptmalloc [Gloger]); and optimization of the application design by removing a number of heap allocations/deallocations respectively. The number of heap allocations/ deallocations was reduced by introducing object-pools for commonly used object types, and by replacing heap variables with stack variables. The time spent on re-designing the BGw was rather limited (one week). The parallel heap approach resulted in dramatic scale-up improvement. The optimization of the application design also resulted in a dramatic scale-up improvement. This approach also improves performance when the application is executed on a single-processor computer.

Figure 1. The processing capacity of BGw (version 3) on an 8-way SMP.

#### Paper II: Memory Allocation Prevented Telecommunication Application to be Parallelized for Better Database Utilization

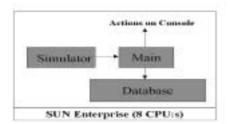

This paper replicates the results of paper I on yet another application, the Fraud Control Center (FCC). The latter application has been developed by Ericsson and is part of an anti-fraud system that combats mobile telephone fraud with the aid of real-time analysis of network traffic [Lundin et al. 96]. It is based on a commercial relational database management system [Connolly at al. 96]. The parallelization of the FCC application using multithreaded programming was not only designed to scale-up the multithreaded part of the application but also to improve the performance of the database system [XI].

A database server cannot usually be fully utilized using a single client, particularly if the database server is executed on a symmetric multiprocessor. Multithreading makes it possible for an application implemented as a single process to have multiple database clients. This study shows, however, that object-oriented development - more specifically, its impact on dynamic memory management - prevented

the application from benefiting from multiple database clients. Although the database module performed most of the work, the limiting factor in the FCC was the poor performance of the multithreaded client part. Our use of a parallel heap implementation (ptmalloc [Gloger]) for optimizing the dynamic memory management in the FCC proved successful. We also showed that the performance characteristics of the multithreaded client version using ptmalloc were very similar to a version in which the clients executed in separate processes.

# Paper III: Maintainability Myth Causes Performance Problems in Parallel Applications

Papers I and II show that multithreaded applications developed with object-oriented methodologies have a potential bottleneck within their dynamic memory management. The main reason is that object-oriented methodologies tend to increase the number of dynamic memory allocations. Our evaluations also show that restricting the use of object-oriented design significantly reduces the risk of congestion within the dynamic memory management.

Using interviews with the developers of the FCC as a base, paper III identifies maintainability together with flexibility as an indirect reason for the large number of dynamic memory allocations occurring. The assumption was that adaptable object designs (e.g. design patterns [Gamma et al. 97]) would give a more maintainable application.

An alternative design, based on rigid but exchangeable components, was, however, implemented and evaluated. Maintainability was predicted using a state-of-the-art method [Bengtsson et al. 99]. The evaluation results show that the alternative design has superior performance characteristics as well as higher maintainability. These findings show that the design decision chosen was based on an assumption which subsequently proved invalid, i.e. the performance problems in FCC were based on a myth.

This is a joint paper written in collaboration with PerOlof Bengtsson. The latter performed the maintenance evaluations; the interviews were carried out together.

The paper is also available in an earlier version [XIV].

## Paper IV: A Simple Process for Migrating Server Applications to SMPs

The first three studies (papers I, II and III) all show a bottleneck within the dynamic memory management. The studies also showed that the bottleneck was not anticipated by the developers and resulted in a substantial decrease in performance. In all cases, however, the bottleneck could easily be removed by choosing an alternative design strategy; it could also be substantially reduced by applying a dynamic memory allocator optimized for SMPs. Further, all applications had been developed under approximately the same pre-conditions. The developers were thoroughly trained in modern software engineering, including object-oriented design, frameworks and design patterns. The applications include a substantial amount of third-party tools and software. The performance requirements were mainly met by using the latest in high-performance, off-the-shelf uni-processor hardware. However, higher requirements with regard to performance, or complementary requirements with respect to scalable performance necessitated a migration from a uni-processor to a multiprocessor architecture, i.e., SMP.

Designing efficient applications for SMPs is a vital task since communication and synchronization can easily limit the scale-up to a considerable degree. Efficient strategies for designing and implementing multiprocessor applications are widely recognized [Foster 95]. In this type of application, however, the parallel performance must be balanced against other quality attributes such as maintainability and flexibility.

For developers used to developing maintainable and flexible software but not familiar with parallel hardware architecture and parallel software, making the right trade-offs for higher multiprocessor performance can be very difficult, if not impossible. However, our results show that large improvements can be made by just making the developers aware of the problem with dynamic memory allocations on SMPs.

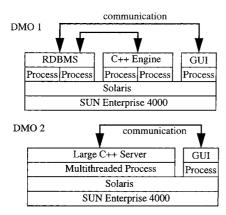

Using the results from papers I, II and III and a study of a third application (DMO), I have defined a simple process based on ten guidelines [XII]. The process is designed with the aim of helping designers of applications to become more efficient in creating a balance between SMP performance and maintainability.

## Paper V: Quality Attribute Conflicts - Experiences from a Large Telecommunication Application

Previous research (papers I, II, III and IV) has shown that a strong focus on quality attributes such as maintainability and flexibility can result in less efficient applications, at least from a performance perspective. One of the main reasons for this is that applications developed using these new methodologies are more general and dynamic in their design. This is an advantage in terms of maintainability but gives poorer application performance. As a result, the ambition of building maintainable systems often results in poor performance.

Performance is often gained by customizations, i.e., by using less generic solutions. Common examples are application-specific buffering of persistent data and bypassing layers in multi-layer architectures. Customization of functions tends to increase the amount of application code since code that is normally located in the operating system or in third party software must be dealt with on an application level. Work carried out by other researchers indicates that maintenance costs are strongly related to the amount of application code [Granja & Barrancp-Garcia 97] [Li & Henry 93].

One hypothesis is thus that the quality attribute "conflict" seen in previous case-studies is bidirectional i.e., if applications developed with a strong focus on run-time qualities such as performance and availability uncover unknown software design conflict, with maintainability problems as a result. Note that I now also introduce the notion of availability into my reasoning. A second hypothesis is that the best balance between performance and availability on the one hand and maintainability on the other is obtained by focusing on maintainability in the software design, and by using high-end hardware and software execution platforms for solving the majority of the performance and availability issues. It has at least been shown that it is relatively easy to achieve high performance in applications developed with a strong focus on maintainability with the aid of SMPs [IV].

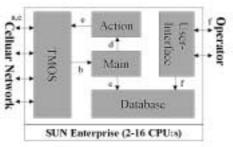

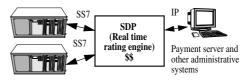

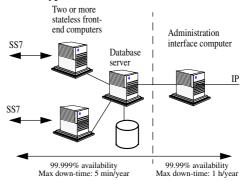

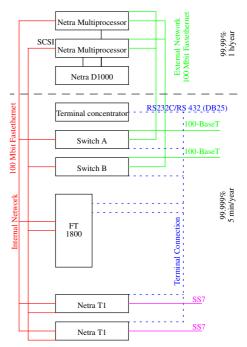

The aim behind paper V was to check if the above two hypotheses were correct. This was made possible by studying yet another telecommunication application. The latter is part of a system which rates pre-paid subscribers in real-time. The system has been developed for the cellular market by the Ericsson telecommunication company.

Rating of pre-paid subscribers is a mission-critical task which requires extremely high performance and availability.

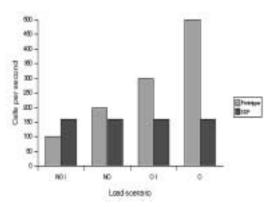

The first of three results related to source code categorization, which showed that 85% of the source code was dictated by performance or availability. A result which supports the first hypothesis. The second result was a prototype developed according to a three-step process prioritizing maintainability. The prototype contained less than 7,000 LOC (lines of code) and was capable of handling three times more calls than the original application. The additional cost for the platform was 20-30% for the prototype as compared to the old application. A result which supports the second hypothesis. The most useful design strategies were extracted as three guidelines, which comprised the third result.

This study was carried out with the aid of Jonas Matton. The latter performed the source-code measurements as part of his master's thesis.

#### Paper VI: Attacking the Dynamic Memory Problem for SMPs

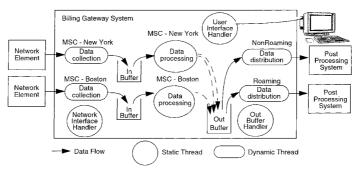

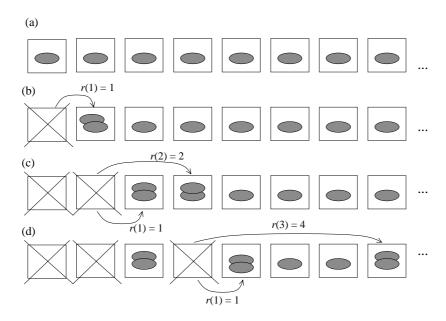

Dynamic memory management has constituted the most serious serialization bottleneck in many of the applications studied. The dynamic memory problem has been addressed in a number of ways. In this paper, we summarize and structure our experiences of some of these. There are two basic ways of attacking the problem: either you reduce the cost of using dynamic memory, or you reduce the use of short-lived dynamic memory allocations (see Figure 2 on the following page).

The problem can also be addressed at different levels, i.e. the operating system, the implementation, and the software architecture and design levels. Each of the investigated ways of attacking the dynamic memory problem has its own particular advantages and disadvantages.

I argue that one should focus on the operating system level when dealing with an existing code, and on the software architecture level when developing new applications.

#### Attacking the dynamic memory problem for SMPs

| Level \ Type               | Reduce cost                                       | Reduce usage                           |

|----------------------------|---------------------------------------------------|----------------------------------------|

| Architecture and<br>Design | Processes instead of threads                      | Rigid but exchange-<br>able components |

| Implementation             | Object pools<br>(Customized allocator)            | Use stack instead of heap              |

| Operating System           | Parallel allocator<br>(General propose allocator) | No method found                        |

**Figure 2.** Categorization of methods which can be used to attack the dynamic memory problem on an SMP.

## Paper VII: A Method for Automatic Optimization of Dynamic Memory Management in C++

Paper VI points out that the simplest way to attack the dynamic memory problem is to optimize the C library memory allocation routines. However, the results discussed in paper I show that it can be more efficient to address the problem on the source code level, i.e., modify the application's source code. Such an approach makes it possible to achieve more efficient and customized memory management. To implement and maintain such design and source code optimizations is, however, both a laborious and costly since the procedure must be done manually.

Reducing the use of short lived memory allocation gives the best results in terms of performance. Attacking the problem at an operating system level is the most effective method in terms of man hours. Consequently, the most favorable method is, from our perspective, found down to the right in the matris (Figure 2), the vacant spot. A challenge is thus to fill this vacancy.

Paper III shows that the large amount of dynamic memory is to a considerable extent the result of designers' attempts to increase maintainability, i.e., make the application easier to adjust to new or modified requirements. Such adjustments are not usually made in runtime; temporal locality (defined in the paper) will thus characterize the run-time behavior of the dynamic memory allocations in the applications.

This paper presents an implementation of a pre-processor based method named Amplify which reduces the usage of small and short-lived memory allocations in (object-oriented) C++ applications. Amplify does this by speculating on the temporal locality of dynamic memory allocations. Test results show that Amplify can obtain significant speed-up in synthetic applications, and that it can also be effective on real applications (BGw). The methods is patent pending [XVIII].

This paper was complied with the help of Per Lidén. The latter aided me with the design and implementation of the pre-processor.

The increasing popularity of Java makes it interesting to determine if Java applications have similar performance problems with dynamic memory as C++ has, and if the same method, effective for C++ applications, is also useful for applications written in Java. To do this is, however, a not unproblemetic task since there are a number of fundamental differences between C++ and Java, e.g. language constraints, garbage collection and the virtual machine concept. These differences make it not only necessary to re-implement Amplify in Java, but also to reconsider some of the basics of the method (see [XVII]).

# Paper VIII: Recovery Schemes for High Availability and High Performance Cluster Computing

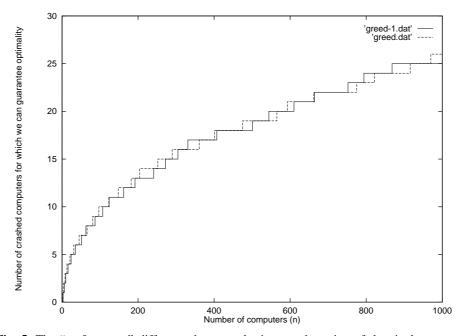

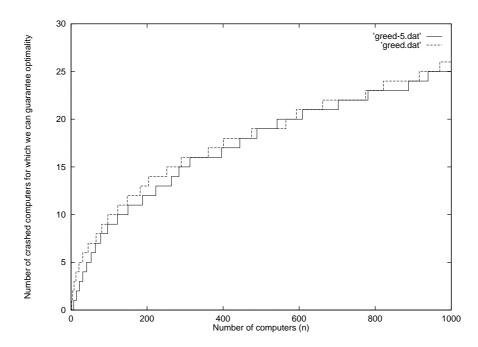

One way of obtaining high-availability is to distribute an application in a cluster or a distributed system [Pfister 98]. If a computer breaks down, the functionality performed by that computer will be handled by some other computer in the cluster. Many cluster vendors support this kind of fault recovery, e.g., Sun Cluster [Sun Cluster], MC/ServiceGuard (HP) [MC/ServiceGuard], TrueCluster (DEC) [TrueCluster], HACMP (IBM) [Ahrens et al. 95], and MSCS (Microsoft) [Vogels et al.]. One way to define how functionality is redistributed in the clusters is to define recovery schemes. Lundberg et al. have proposed a recovery scheme that is optimal for a number of important cases and which defines a bound on the performance of the recovery schemes for any number of computers. In this paper we have attacked the same problem; we have, however, reformulated the problem definition, and suggested a simple algorithm which generates recovery schemes that are better than

those defined in [Lundberg & Svahnberg 99]. The bounds of the recovery schemes have been decided using the same methods as in [X].

This is a joint paper written in collaboration with Lars Lundberg. My contribution was the reformulation of the problem and the definition of the algorithm.

#### 5. Related Work

This section presents prior and related work. It has been divided into three parts: quality attributes, dynamic memory allocators and recovery schemes for high-availability clusters. Additional prior and related work is presented in the individual papers (see paper section)

#### 5.1 Quality Attributes (Factors)

The concept of quality factor originated in the late 1970s in conjunction with the research and development of software measurement technology. The factors provide the definition of quality required for a software product. The early work consisted of identifying sets of factors or characteristics, related attributes and criteria, and metrics. Further developments during the 80s have refined the factors or added additional factors for consideration. A survey of identified factors, attributes, criteria and metrics can be found in [McCall 94], where they are assembled into a framework with the aim of capturing relations between quality factors, related attributes and criteria, and metrics. It is interesting to note that the effectivity quality factor is in conflict, or, as McCall so logically argues, "can be more costly to achieve together" with all other factors except correctness and reliability (see Figure 5, p. 967 in [McCall 94]). The framework also defines relations between quality factors and system characteristics, see Table 6, p. 968. Of eleven listed system characteristics, only two, according to McCall, are related to efficiency; these are real-time applications and on-line usage. Introduction of software quality factors such as maintainability, flexibility and portability into real-time applications can thus be expected to be very costly. Further, the introduction of on-line usage into applications which have previously been executed off-line, is, as the framework shows, likely to lead to quality factor conflicts.

The conclusions outlined in Mcall's tables and classification comply well with the emerging conflicts I have found in the applications studied in this thesis.

Finding the right balance of quality attributes is thus of utmost importance. One possible method is to reduce the conflicts already in the requirement setting. Research has been conducted in this area, and methods and knowledge-base tools have been developed with the aim of

helping users, developers, and customers to analyze and identify conflicts among the requirements [Boehm & In 99]. However, the conflicts found using these methods and tools are far from complete, and even if the conflicts are identified, they may be unavoidable and must thus be dealt with when the system is designed, dealing with design conflicts is therefore still highly relevant.

A number of methods developed to identify conflicts on an architecture level have been proposed. Kazman et al. have developed the Architecture Trade-off Analysis Method (ATAM) which addresses the need for trade-offs between different quality attributes [Kazman et al. 99]. The main goal of ATAM is to illuminate risks early on in the design process. However, ATAM does not contain any concrete guidelines regarding software architecture and design. Lundberg et al. have developed a set of guidelines and a simple design process that can be used for making design and architectural trade-offs between quality attributes [XIII] [XVI]. Kruchten has suggested the "4+1 View Model" which makes it possible to communicate and engineer different aspects of a software system, e.g., development as well as run-time aspects [Kruchten 95]. In this way, the probability of identifying conflicts can be increased. The goal of my work has not been to investigate or make a survey of quality attribute "conflicts"; instead, I have studied software design conflicts; the quality attribute "conflicts" are what give my work context and relevance.

#### 5.2 Dynamic Memory Allocators for C++ and SMPs

Dynamic storage allocation (DSA) and memory management (DMA) is a large area. Ben Zorn maintains a repository with related information [Zorn]. This repository includes information about explicit allocation mechanisms such as malloc/free and automatic storage reclamation algorithms such as garbage collection. Wilson et al. have made an excellent survey of literature and allocators [Wilson et al. 95]. Berger et al. have recently presented a flexible and efficient infrastructure for building memory allocators based on C++ templates and inherence. The main intention is to help programmers to build customized allocators [Berger et al 01]. Reports are also available on hardware support for dynamic memory management [Chang et al. 00]. Henceforth, this section will only focus on malloc/free allocators design for SMPs.

The allocator designed by Doug Lea is both fast and efficient [Lea]. However, the original version is neither thread-safe nor scalable on SMPs. Using Doug Lea's implementation, Wolfram Gloger created a thread-safe and scalable version called ptmalloc [Gloger]. The allocator is based on a multiple number of sub-heaps. When a thread is about to make an allocation it "spins" over a number of heaps until it finds an unlocked heap. The thread will use this heap for the allocation and for all future allocations. If an allocation fails, the thread "spins" for a new heap. Since the operating system normally keeps the number of thread migrations low this implementation works well for a number of applications. However, when the number of threads is larger than the number of processors, ptmalloc may prove unpredictable in terms of efficiency. We have successfully used this heap implementation in our own studies.

An SMP version of SmartHeap is commercially available [Microquill]. We have not had the opportunity to test this implementation on our synthetic programs since the software is not readily accessible. During our test on BGw, however, we were able to make some benchmark tests on this allocator.

Hoard [Berger et al. 00] is another allocator optimized for SMPs which we successfully used in one of our studies. This allocator focuses on avoiding false memory sharing and blowup in memory consumption. The allocator is scalable. However, we have found that Hoard has problems when threads frequently migrate between processors, e.g. when the number of threads is larger than the number of processors.

LKmalloc [Larson & Krishan 98], developed by Larsson and Krishnan, is yet another parallel memory allocator (this has not been investigated by us). It is intended to be fast and scalable in traditional applications as well as long-running server applications executed on multiprocessor hardware.

Prior to ptmalloc, Hoard, LKmalloc etc., - all of which are relatively recent contributions - there is little work available on parallel memory allocators.

The major difference between my work on dynamic memory allocation and the work described above is that I do not address the area of dynamic memory management in general. My concern is the specific problems which occur when aiming simultaneously at maintainability and performance, i.e., how design strategies for maintainability stress

the use of dynamic memory and how to avoid this becoming a bottleneck in applications running on SMPs.

# 5.3 Recovery Schemes for High-Availability Clusters

The problem of finding optimal recovery schemes for clusters of computers seems to be NP-hard [Garey & Johnson 79]. Lundberg et al. have proposed a recovery scheme which is optimal for a number of important cases and have defined a bound on the performance of the recovery schemes for any number of computers [Lundberg & Svahnberg 99]. Similar types of bounds have proven useful for other NP-hard resource allocation problems [Lundberg & Lennerstad 98].

# 6. References

- [Ahrens et al. 95] G. Ahrens, A. Chandra, M. Kanthanathan and D. Cox, "Evaluating HACMP/6000: A Clustering Solution for High Availability Distributed Systems", in Proceedings of the 1995 Faoult-Tolerant Parallel and Distributed System Symposium, pp 2-9, 1995.

- [Bengtsson et al. 99] P. Bengtsson, J. Bosch, "Architecture Level Prediction of Software Maintenance", in Proceedings of 3rd European Conference on Maintenance and Reengineering, Amsterdam 1999.

- [Berger et al. 00] E. D. Berger, K. McKinley, R. Blumofe and P. Wilson, "Hoard: A Scalable Memory Allocator for Multithreaded Applications", in Proceedings of the 9th International Conference on Architectural Support for Programming Languages and Operating Systems, Cambridge, MA, November 2000.

- [Berger et al 01] E. D. Berger, B. G. Zorn, and K. S. McKinley, "Composing High-Performance Memory Allocators", in Proceedings of the ACM SIGPLAN Conference on Programming Language Design and Implementation, Snowbird, Utah, June 2001.

- [Boehm & In 99] B. Boehm and H. In, "Identifying Quality-Requirement Conflicts", *IEEE Computer*, August 1999, pp. 27-33.

- [Chang et al. 00] J. M. Chang, W. Srisa-an, C. D. Lo, and E. F. Gehringer, "Hardware support for dynamic memory management", in Proceedings of the Workshop for Solving the Memory-Wall Problem, at the 27th International Symposium on Computer Architecture, Vancouver, BC, June 2000.

- [Connolly at al. 96] T.Connolly, C. Begg and A. Strachan, "Database Systems", Addison-Wesely, 1996.

- [Foster 95] I. Foster, "Designing and Building Parallel Programs", Addison Wesley, 1995.

- [Gamma et al. 97] E. Gamma, R. Helm, R. Johnson, J. Vilssides, "Design Patterns", Addison-Wesley, 1997.

- [Garey & Johnson 79] M. R. Garey and D. S. Johnson, "Computers and Interactability", W. H. Freeman and Company, 1979.

Sofware Design Conflicts

- [Gloger] W. Gloger, "Dynamic memory allocator implementations in Linux system libraries", http://www.dent.med.uni-muenchen.de/-wmglo/malloc-slides.html (site visited August 14th, 2001).

- [Granja & Barrancp-Garcia 97] J. C. Granja-Alvarez and J. Barrancp-Garcia, "A Method for Estimating Maintenance Cost in a Software Project: A Case Study", *Journal of Software Maintenance: Research and Practice*, John Wiley & Sons, Volume 9, pp. 166-175, 1997.

- [Hwang & Xu 98] K. Hwang, Z. Xu, "Scalable and Parallel Computing", WCB/McGraw-Hill, 1998.

- [IEEE 90] IEEE, "IEEE Standard Glossary of Software Engineering Terminology", IEEE Stad 610.12-1990, 1990.

- [**ISO 00**] ISO 9126, "Software Qualities", *SO/IEC FDIS 9126-1:2000(E)*, 2000.

- [Kajko-Mattson 01] M. Kajko-Mattson, "Can we Learn Anything from Hardware Preventive Maintenance", in Proceedings of the 7:th IEEE International Conference on Engineering of Complex Computer Systems, Skövde, Sweden, pp. 106-111, June 2001.

- [Kazman et al. 99] R. Kazman, M. Barbacci, M. Klein, S.J. Carrière, "Experience with Performing Architecture Tradeoff Analysis", in Proceedings of the International Conference on Software Engineering, Los Angeles, USA, May 1999, pp. 54-63.

- [Kruchten 95] P. Kruchten, "The 4+1 View Model of Architecture", *IEEE Software*, November 1995, pp. 42-50.

- [Larson & Krishan 98] P. Larson and M. Krishan, "Memory Allocation for Long-Running Server Applications", in Proceedings of the International Symposium on Memory Management, Vancouver, British Columbia, Canada, October, 1998.

- [Lea] D. Lea, "A Memory Allocator", http://g.oswego.edu/dl/html/malloc.html (site visited August 14th, 2001).

- [Lewis 96] B. Lewis, "Threads Primer", Prentice Hall, 1996.

- [Li & Henry 93] W. Li and S. Henry, "Object-Oriented Metrics that Predict Maintainability", *Journal of Systems Software*, 1993;23, pp. 111-122.

- [Lundberg & Lennerstad 98] L. Lundberg and H. Lennerstad, "Using Recorded Values for Bounding the Minimum Completion Time in Multiprocessors", *IEEE Transactions on Parallel and Distributed Systems*, pp. 346-358, April, 1998.

- [Lundberg & Svahnberg 99] L. Lundberg and Charlie Svahnberg, "Optimal Recovery Schemes for High-Availability Cluster and Distributed Computing", in Proceedings of the 6th International Australasian Conference on Parallel and Real-Time Systems, Melbourne, Australia, pp. 153-167, November 1999 (Springer Verlag).

- [Lundin et al. 96] C. Lundin, B. Nguyen and B. Ewart, "Fraud management and prevention in Ericsson's AMPS/D-AMPS system", *Ericsson Review* No. 4, 1996.

- [McCall 94] J. A. McCall, "Quality Factors", Encyclopedia of Software Engineering, Volume 2, pp. 958-969, 1994.

- [Microquill] Microquill, "SmartHeap for SMP", http://www.microquill.com/smp, (site visited August 22nd, 1999).

- [MC/ServiceGuard] MC/ServiceGuard, "Managing MC/ServiceGuard for HP-UX 11.0", http://docs.hp.com/hpux/ha.

- [Pigoski 97] T. M. Pigoski, "Practical Software Maintenance", Wiley Computer Publishing, 1997, table 3.1, p. 31.

- [Pfister 98] G. F. Pfister, "In Search of Clusters", Prentice Hall, 1998.

- [Roberts & Johnson 96] D. Roberts, RE. Johnson, "Evolving frameworks: a pattern language for developing object oriented frameworks", *in Pattern Languages of Programming Design 3*, Addison-Wesley Publishing Co.:Reading MA; pp. 471-486, 1996.

- [Sun Cluster] Sun, "Sun Cluster 2.1 System Administration Guide", Sun Microsystems, 1998.

- [TrueCluster] DEC, TrueCluster 2.1 System Administration Guide, Digital Equipment Corporation 1998, http://www.unix.digital.com/faqs/publications/cluster\_doc/cluster\_16.

- [Vogels et al.] W. Vogels, D. Dumitriu, A. Argawal, T. Chia and K. Guo, "Scalability of the Microsoft Cluster Service", http://www.cs.cornell.edu/rdc/mscs/nt98.

Sofware Design Conflicts

- [Wilson et al. 95] R. Wilson, M. Johnstone, M. Neely and D. Boles, "Dynamic storage allocation: A survey and critical review", in Prodeedings of the 1995 International Workshop on Memory Management, Kinross, Scotland, UK, 1995 (Springer Verlag)

A slightly updated version of this paper can be found at: ftp://ftp.cs.utexas.edu/pub/garbage/allocsrv.ps

- [Zorn] B. Zorn, "Malloc and GC implementations", http://www.cs.colorado.edu/~zorn/Malloc.html, (site visited August 14th, 2001).

# **Paper Section**

Optimizing Dynamic Memory Management in a Multithreaded Application Executing on a Multiprocessor

Ι

Memory Allocation Prevented Telecommunication Application to be Parallelized for Better Database Utilization

Ш

Maintainability Myth Causes Performance Problems in Parallel Applications

Ш

A Simple Process for Migrating Server Applications to SMPs

IV

Quality Attribute Conflicts - Experiences from a Large Telecommunication Application

V

Attacking the Dynamic Memory Problem for SMPs

VI

A Method for Automatic Optimization of Dynamic Memory Management in C++

VII

Recovery Schemes for High Availability and High Performance Cluster Computing

VIII

# I

# Paper I

# Optimizing Dynamic Memory Management in a Multithreaded Application Executing on a Multiprocessor

# Daniel Häggander and Lars Lundberg

27th International Conference on Parallel Processing Minneapolis, USA August 1998

# Optimizing Dynamic Memory Management in a Multithreaded Application Executing on a Multiprocessor

Daniel Häggander Ericsson Software Technology AB S-371 23 Karlskrona, Sweden Daniel.Haggander@epk.ericsson.se Lars Lundberg University of Karlskrona/Ronneby S-372 25 Ronneby, Sweden Lars.Lundberg@ide.hk-r.se

#### Abstract

The Billing Gateway (BGw) is a large multithreaded object oriented C++ application running on Sun Solaris. Due to frequent allocation and deallocation of dynamic memory, the initial implementation of this system suffered from poor performance when executed on a multiprocessor.

In this paper we compare two approaches for improving the performance of BGw. First we replace the standard Solaris heap with a parallel heap. In the second approach we optimize the application code by removing a number of heap allocations/deallocations. In order to do this, we introduce memory pools for commonly used object types and replace some heap variables with stack variables.

The parallel heap approach resulted in a dramatic speedup improvement. The optimization of the application code did also result in a dramatic speedup improvement. For this approach the performance using a single-processor computer was also increased by a factor of eight. The optimizations took approximately one week to implement.

# 1. Introduction

Today, multiprocessors are used in a number of applications. Multithreaded programing makes it possible to write parallel applications which benefit from the processing capacity of multiprocessors. However, some parallel applications suffer from large run-time overhead and serialization problems when using multiprocessors. The speedup for multithreaded applications is usually good when the first processors are added. When more processors are added, the speedup curve increases more slowly. In some cases the speedup can actually start to decrease when we add more processors.

One serialization problem is sequential dynamic memory management. Moreover, most dynamic memory handlers are implemented without any consideration of multiprocessing specific problems, e.g. false memory sharing [2].

Object-orientation helps the programmer to develop large and maintainable software. Unfortunately, this use of object-orientation often results in an more intensive use of dynamic memory, making the dynamic memory performance problem worse.

The standard implementation of dynamic memory is often rather inefficient. A number of more efficient implementations have been developed, e.g. SmartHeap [4] and Heap++ [5]. The most common strategy is to use different allocation algorithms depending on the size of the requested memory. QuickHeap is a typical example [7].

An optimized heap often results in better performance for none-parallel applications. However, a performance evaluation of a weather forecast model [3] showed that a heap implementation which was efficient on a single-processor caused performance problems on a multiprocessor.

For multiprocessor systems ptmalloc [6] can be efficient. ptmalloc is a heap implementation which can perform several allocations and deallocations in parallel. The ptmalloc implementation is a version of Doug Lea's malloc implementation that was adapted for multiple threads by Volfram Gloger, while trying to avoid lock contention as much as possible.

The Billing Gateway (BGw) is a system for collecting billing information about calls from mobile phones. The system is a commercial product and it has been developed by the Ericsson telecommunication company. BGw is written in C++ [11] (approximately 100,000 lines of code) using object-oriented design, and the parallel execution has been implemented using Solaris threads. The system architecture is parallel and we therefore expected good speedup when using a multiprocessor. However, the actual speedup of BGw was very disappointing.

By using the BGw as an example, we explain why dynamic memory management can cause poor speedup when using a multiprocessor, particularly for object oriented programs. We also describe and evaluate two methods which dramatically improved the speedup of the BGw using a Sun multiprocessor with eight processors. These two methods

are: using a parallel heap implementation and redesigning memory usage within the application code, respectively.

The rest of the report is structured in following way: Section 2 describes the BGw and its speedup problem. Section 3 describes the dynamic memory performance problem in detail. In section 4 a parallel heap implementation is investigated. Section 5 describes a redesign which reduces the number of heap allocations. Section 6 concludes the paper.

#### 2. Billing Gateway (BGw)

#### 2.1. Overview

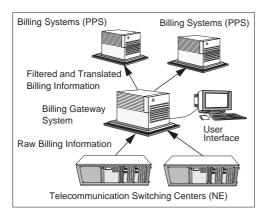

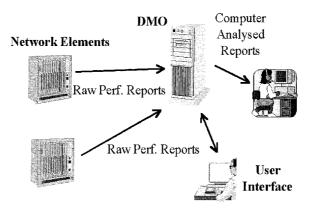

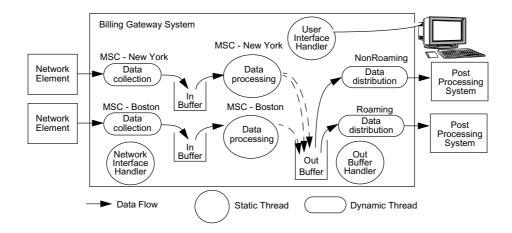

BGw transfers, filters and translates raw billing information from Network Elements (NE), such as switching centers and voice mail centers, in the telecommunication network to billing systems and other Post Processing Systems (PPS). Customer bills are then issued from the billing systems (see figure 1). The raw billing information consists of Call Data Records (CDRs). A CDR contains information about a call (in certain rare cases information about a call may be split up into several CDRs, e.g. when the call is very long). Each CDR is 175-225 bytes long. The CDRs are continuously stored in files in the network elements. With certain time intervals or when the files have reached a certain size, these files are sent to the billing gateway.

Figure 1. The Billing Gateway system.

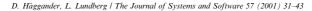

There is a graphical user interface connected to the gateway system. In this interface the different streams of information going through the gateway are visualized as a directed graph, i.e. each billing application is represented as a graph. There are four major types of nodes in the application graphs.

Network element (NE) and post processing system (PPS) nodes represent external systems which communi-

cate with the gateway, e.g. each switching center is represented as a NE node and each billing system is represented as a PPS node. There may be any number of NE and PPS nodes in an application.

The information streams in an application start in a NE node. An information stream always ends at a PPS node. Using a Filter node, it is possible to filter out some records in the information streams. In some cases the record format in the information streams has to be changed, e.g. when the post processing systems do not use the same record format as the network elements. Formatter nodes make it possible to perform such reformatting.

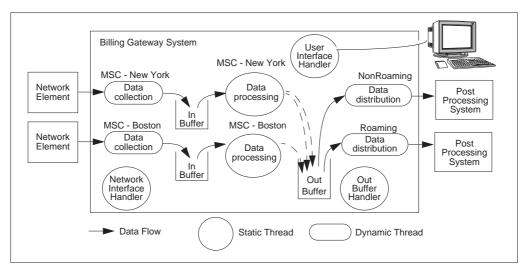

Figure 2 shows an application where there are two network elements producing billing information (the two leftmost nodes). These are called "MSC - New York" and "MSC - Boston" (MSC = Mobile Switching Center). The CDRs from these two MSCs are sent to a filter called "is-Billable". There is a function associated with each filter, and in this case the filter function evaluates to true for CDRs which contain proper information about billable services. CDRs which do not contain information about billable services are simply filtered out. The other CDRs are sent to another filter called "isRoaming". In this case, there are two stream going out from the filter.

Figure 2. BGw configuration window.

The function associated with "isRoaming" evaluates to true if the CDR contains information about a roaming call (a roaming call occurs when a customer is using a network operator other than his own, e.g when travelling in another country). In this case, the record is forwarded to a formatter, and then to a billing system for roaming calls. If the filter function evaluates to false, the record is sent to a formatter and billing system for non-roaming calls. The billing systems are represented as PPS nodes.

The record format used by the billing systems differs from the record format produced by the MSCs. This is why the CDRs coming out of the last filter have to be translated into the record format used by the billing system before they can be sent from the gateway system to the billing systems.

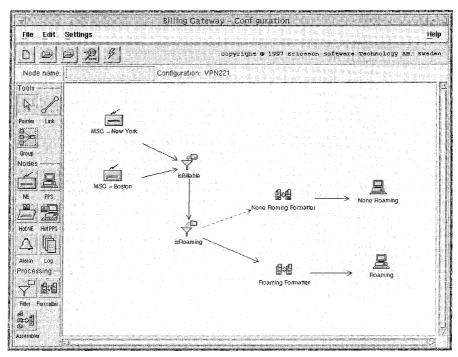

Figure 3. The thread structure of Billing Gateway.

The graph shown in figure 2 is only one example of how billing applications can be configured. The system can handle a large number of combinations of network elements, filters, formatters and post processing systems.

## 2.2. Implementation

Figure 3 shows the major threads for the application shown in figure 2. In order not to complicate the figure, some threads which monitor disk and memory usage etc. have been left out.

When there is no flow of data through the gateway, the system contains a number of static threads. When there is a flow of information going through the system, some additional threads are created dynamically.

When a network element wants to send a billing file to the gateway it starts by sending a connect message. This message is handled by the Network Interface Handler thread. This thread checks if the message is valid and determines the identity of the requesting network element. If the message is valid, a data collection thread is created. This thread reads the file from the network element and stores it on disk. When the complete file has been stored the data collection thread notifies the thread that shall process the data, and then the data collection thread terminates.

The data processing, i.e. the part of BGw that does the actual filtering and formatting, is implemented in a different way. When a configuration is activated, BGw creates one data processing thread for each NE node within the configuration (see figure 3). Every thread is bound to a certain NE,

i.e a data processing thread can only process files which have been collected by the corresponding NE.

For the application in figure 2 each file of billing information from the network elements may generate a transmission of either zero, one or two files of billing information to the post processing systems. If all CDRs are filtered out as unbillable, no file is generated by the data processing thread. If all billable CDRs are either roaming or non-roaming, one file is generated for the billing system for roaming or non-roaming calls. If the MSC file contains billable CDRs for both roaming and non-roaming calls, one file is generated for each of the two billing systems. The files generated by the data processing threads are put into an outbuffer. When a file has been generated, the data processing thread notifies the Out Buffer Handler thread. The data processing thread then starts to process the next file in its In Buffer. If the In Buffer is empty, the thread waits until the next files has been collected.

The Out Buffer Handler is notified that a new file has been put into its buffer and a data distribution thread is created. This thread sends the file to the corresponding post processing system. The data distribution thread terminates when the file has been transmitted.

# 2.3. Performance

Billing Gateway versions 1 and 2 have been evaluated, using a Sun Sparc Center 2000 and a Sun Enterprise 4000 with eight processors [10]. These evaluations showed that a good speedup was achieved when the first processors were

added. When more processors were added, the speedup curve started to fall off. The speedup curves for BGw 1 and BGw 2 can be seen in figure 4. The configuration is the same as in figure 2 with the exception that there are eight network elements (MSCs) instead of two.

BGw 3 is the latest version of the Billing Gateway. This version has some new features. The most significant one is a new language which makes is possible to define more complex filters and formatters. The new language is of "C" style with sub-functions and local variables. The new language makes it easier to adapt BGw to new environments and configurations. However, the speedup of BGw 3 was extremely poor (see figure 4).

Figure 4. The speedup of the 3 BGw releases.

Previous investigations [3] have shown that dynamic memory can cause performance problems for multithreaded applications executing on multiprocessors. To find out if the dynamic memory caused the performance problem in BGw 3, an additional test was made.

One of the new features in BGw 3 which uses dynamic memory very frequently is the run-time interpreter of the filter- and formatter-language. The implementation of the language interpreter uses memory from the heap to store the local variables. The design of the application is made in such a way that at least one sub-function call was done when a CDR was processed by a filter or a formatter. This design led to a very intensive use of the heap, even for small configurations.

Another feature which uses dynamic memory frequently is the CDR decoder. More exactly, the decoding of CDRs containing dynamic structures of information. The implementation of the decoding algorithm is (more or less) the same in BGw 1, 2 and 3.

In order to test if dynamic memory management caused the speedup problems, the problematic CDRs were removed from the test files. Also, the filters and formatters used in the test was redefined in such a way that the number of sub-function calls and the use of local variables was minimized. The speedup of the adapted configuration and the new work-load was almost linear, i.e. almost optimal. Consequently, dynamic memory management caused most of the speedup problems in BGw 3.

In the next section we will discuss why dynamic memory management causes such large performance problems.

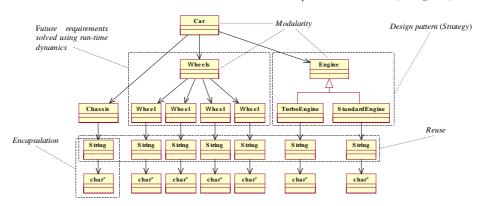

#### 3. Dynamic memory management

Some features within the C++ language, such as dynamic binding [11] make it possible to implement a more maintainable software design. This type of design often use dynamic memory to become as general as possible. Reuse issues, such as class libraries and object oriented frameworks [9], advocate a general design and implementation, often resulting in very frequent allocation and deallocation of dynamic memory.

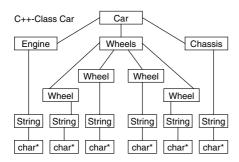

In C++, dynamic memory is allocated via the operator new. The operator returns a pointer to an allocated memory area The memory is then deallocated by the operator delete. Most compilers simply map these operators directly to the malloc() and free() functions of the standard C library. Consequently, C++ applications which have been developed to be general and reusable, use the malloc() and the free() functions very frequently. Figure 5 shows examples of memory management in C and C++ respectively.

In a multithreaded application, all threads use the same memory [8][13]. This means that all threads use the same heap for dynamic memory allocations. Therefore, the allocation- and deallocation-functions should be reentrant. Otherwise, they have to be protected against simultaneous usage. The C library functions malloc() and free() are usually not reentrant and must therefore be protected. In the Solaris implementation the heap is protected by a global mutex. The mutex is locked on entrance and unlock before returning, making sure that only one allocation or deallocation can be performed at the same time.

A major problem for a multithreaded application running on a multiprocessor, is that only one thread can allocate or deallocation memory at the same time. According to Amdahl's Law, no application can run faster than the total execution time of its sequential parts. For applications where dynamic memory is allocated and deallocated frequently, the dynamic memory management significantly decreases the speedup.

However, even if an application spends all its time allocating and deallocating memory, i.e in malloc() and free(), the speedup should never be less than one, which was the case for BGw 3 (see figure 4). Consequently, there must be some additional explanation.

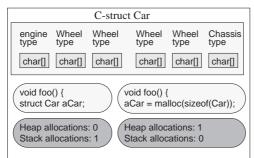

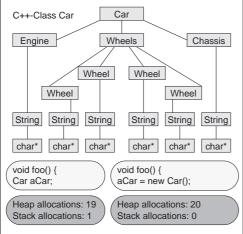

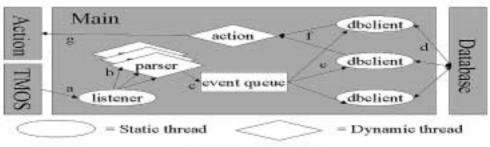

The C programer makes a "struct", in which all the information about the four wheels, the engine and the chassis are stored.

If the car-struct is defined as a local variable, no heap allocation is made. Even if the programer chooses to make a global car, i.e uses the heap, only one heap allocation is necessary.

The C++ programmer often chooses to define a number of sub-objects (this technique improves the reusability). These sub-objects are combined into a car. The programer may also use a class library to handle the names of items, i.e the String object in the figure above. In the constructor of the car object, four wheels, one engine and one chassis are created via the operator new.